# **Chapter 10**

# COMBINATIONAL CIRCUITS

#### **Introduction:**

In a combinational logic circuit, the output is always dependent on the combination of its inputs and, if one of its input condition changes the state of the output also change. Combinational circuits do not have memory, so it does not store any information.

#### Types of combinational circuits:

Combine the logic gate like NAND, NOR or NOT gate we can build large number of combinational circuits. Some relevant combinational circuits are mentioned as follows:

(1) Adders

(2) Multiplexers

(3) De-multiplexers

(4) Decoders

(5) Encoder

(6) Converter

(7) Compartors.

#### **ADDERS CIRCUITS**

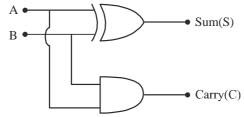

**Half adder:** A logic circuit with two inputs and two outputs that can add two binary digits at a time, producing a sum and a carry, is called a half adder. It is called half adder because to complet binary addition we require two such half adders.

Symbol of half adder

#### Truth table of a half-adder:

| INPUT |   | OUTPUT |   |  |

|-------|---|--------|---|--|

| A     | В | S      | С |  |

| 0     | 0 | 0      | 0 |  |

| 1     | 0 | 1      | 0 |  |

| 0     | 1 | 1      | 0 |  |

| 1     | 1 | 0      | 1 |  |

### Logical expression of HA:

From truth table we can write the expression for sum,

$$S = A\overline{B} + \overline{A}B = A \oplus B$$

The expression for carry, C = AB

# Half adder using XOR and AND gate only:

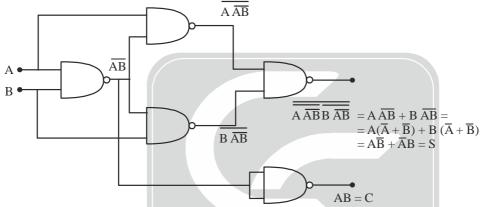

### Half adder using NAND gate only:

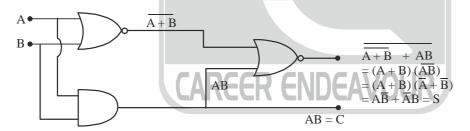

# Half adder using NOR and AND gate only:

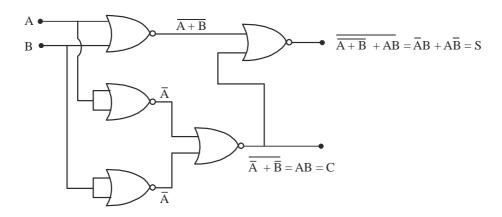

# Half adder using NOR gate only:

#### Full Adder (FA):

A half adder can handle only two bits at a time. But when adding two binary numbers we may have a carry bit coming from the column of lower significant bits. So, the adder circuit must be able to handle three digits at a time. For example, to add the binary numbers,  $A = A_n A_{n-1} A_{n-2} \dots A_2 A_1 A_0$  and  $B = B_n B_{n-1} B_{n-2} \dots B_2 B_1 B_0$  the circuit must be able to add the nth bits  $A_n$  and  $B_n$  with carry  $C_{n-1}$  generated from the addition of (n-1)th order bits. A full adder is a logic circuit with three inputs and two outputs that can add 3 bits at a time and give a sum and carry.

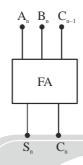

#### Circuit symbol of Full Adder:

#### Truth table of Full Adder:

|       | INPUTS         |           | OUTPUTS |       |  |

|-------|----------------|-----------|---------|-------|--|

| $A_n$ | B <sub>n</sub> | $C_{n-1}$ | $S_n$   | $C_n$ |  |

| 0     | 0              | 0         | 0       | 0     |  |

| 1     | 0              | 0         | 1       | 0     |  |

| 0     | 1              | 0         | 1       | 0     |  |

| 0     | 0              | 1         | 1       | 0     |  |

| 1     | 1              | 0         | 0       | 1     |  |

| 1_    | 0              | 13.       | 0       |       |  |

| 0     | KIC            | 115       | -0      | JUH   |  |

| 1     | 1              | 1         | 1       | 1     |  |

#### Logic expression of full Adder:

From above truth table we can write the expression for sum:

$$\boldsymbol{S}_{n} = \boldsymbol{A}_{n} \overline{\boldsymbol{B}}_{n} \overline{\boldsymbol{C}}_{n-1} + \overline{\boldsymbol{A}}_{n} \boldsymbol{B}_{n} \overline{\boldsymbol{C}}_{n-1} + \overline{\boldsymbol{A}}_{n} \overline{\boldsymbol{B}}_{n} \boldsymbol{C}_{n-1} + \boldsymbol{A}_{n} \boldsymbol{B}_{n} \boldsymbol{C}_{n-1}$$

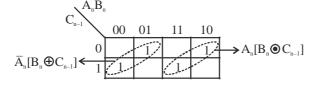

From K-mapping we can write,

$$\begin{split} S_n &= \overline{A}_n \left[ B_n \oplus C_{n-1} \right] + A_n \left[ B_n \odot C_{n-1} \right] \\ &= A_n \oplus B_n \oplus C_{n-1} \end{split}$$

The logic expression for carry